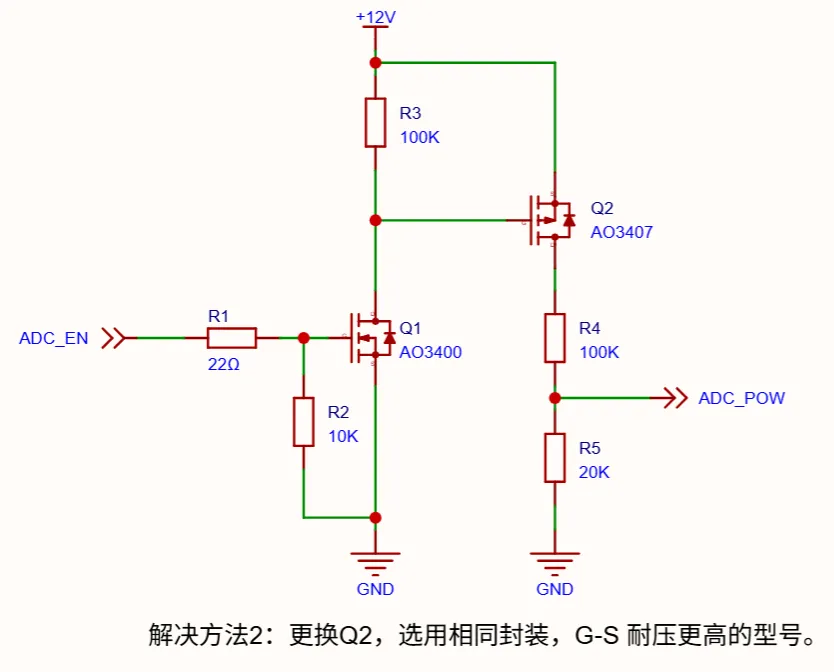

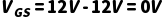

电路原理图:

一、题目

已知上述 ADC 电路,回答以下问题:

1.描述该电路的用途和工作原理;

2.采用该电路的产品在出厂检测时,出现约每 5 台就有 1 台存在漏电的现象(静态电流约 50μA),分析该现象的可能原因;

3.针对上述漏电问题,给出具体的解决措施。

二、解答

1.电路用途与工作原理

该电路为电源电压检测电路,主要应用于电池电量监测场景,通过分压电路将高压电源电压转换为 ADC 可采集的电压信号,实现电源电压的间接测量,同时通过 MOS 管控制测量回路的通断,降低非测量状态下的电能损耗。

具体工作原理分为两种状态:

(1)测量使能状态(ADC_EN 为高电平)

ADC_EN(通常接 MCU 的 GPIO 引脚)输出高电平时,N-MOS 管 Q1 导通,使得 P-MOS 管 Q2 的栅极电压 VG≈0V。此时 Q2 的栅源电压

ADC_EN(通常接 MCU 的 GPIO 引脚)输出高电平时,N-MOS 管 Q1 导通,使得 P-MOS 管 Q2 的栅极电压 VG≈0V。此时 Q2 的栅源电压 ,满足导通条件且驱动能力充足,Q2 完全导通。

,满足导通条件且驱动能力充足,Q2 完全导通。

+12V 电源经 Q2 后,通过 R4(100KΩ)和 R5(20KΩ)构成的分压电路进行分压,分压后 ADC_POW 的电压为:

+12V 电源经 Q2 后,通过 R4(100KΩ)和 R5(20KΩ)构成的分压电路进行分压,分压后 ADC_POW 的电压为:

该电压接入 ADC 采样端口,MCU 通过采集 ADC_POW 的电压值,可反向计算出电源的实际电压,实现电压监测。

该电压接入 ADC 采样端口,MCU 通过采集 ADC_POW 的电压值,可反向计算出电源的实际电压,实现电压监测。

(2)测量关闭状态(ADC_EN 为低电平)

ADC_EN 输出低电平时,N-MOS管Q1截止,Q2的栅极通过R3(100KΩ)上拉至 +12V,此时Q2的栅源电压

ADC_EN 输出低电平时,N-MOS管Q1截止,Q2的栅极通过R3(100KΩ)上拉至 +12V,此时Q2的栅源电压 ,Q2完全截止,整个电压测量回路断开,回路电流为 0,避免非测量阶段的无效电能消耗。

,Q2完全截止,整个电压测量回路断开,回路电流为 0,避免非测量阶段的无效电能消耗。

2.50μA 静态电流漏电现象的原因分析

静态漏电的核心为测量关闭状态下回路未完全截止,存在微小导通电流,逐一排查可能原因如下:

(1)MOS 管栅源电压处于通断临界点(排除)

电路关闭状态下,Q1、Q2 的栅源电压 VGS 均为 0V,而两款 MOS 管的导通阈值电压为 1.2~1.5V,实际 VGS 与导通阈值相差较大,MOS 管不会因临界点问题出现不完全截止,故此原因可排除。

电路关闭状态下,Q1、Q2 的栅源电压 VGS 均为 0V,而两款 MOS 管的导通阈值电压为 1.2~1.5V,实际 VGS 与导通阈值相差较大,MOS 管不会因临界点问题出现不完全截止,故此原因可排除。

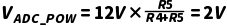

(2)P-MOS 管 Q2(AO3401)因耐压极限问题损坏(核心原因)

结合约 20% 的故障率来看,该问题并非偶然器件故障,而是电路设计中器件参数匹配不当导致的批量性问题。查阅 AO3401 的极限电气参数(Ta=25℃)可知:其栅源电压 VGS 的极限值为 ±12V,而电路中 Q2 导通时的 VGS=-12V,恰好处于器件耐压的临界值。

结合约 20% 的故障率来看,该问题并非偶然器件故障,而是电路设计中器件参数匹配不当导致的批量性问题。查阅 AO3401 的极限电气参数(Ta=25℃)可知:其栅源电压 VGS 的极限值为 ±12V,而电路中 Q2 导通时的 VGS=-12V,恰好处于器件耐压的临界值。

长期工作在栅源电压极限值下,Q2 的栅源极间绝缘层易被击穿,导致器件性能劣化或损坏,出现漏电流,表现为测量关闭状态下仍有 50μA 左右的静态电流,最终体现为产品漏电。

长期工作在栅源电压极限值下,Q2 的栅源极间绝缘层易被击穿,导致器件性能劣化或损坏,出现漏电流,表现为测量关闭状态下仍有 50μA 左右的静态电流,最终体现为产品漏电。

3.漏电问题的解决措施

针对上述核心原因,结合产品量产阶段的成本控制和后续产品的设计优化,给出两种针对性解决方法,分别适用于不同应用场景:

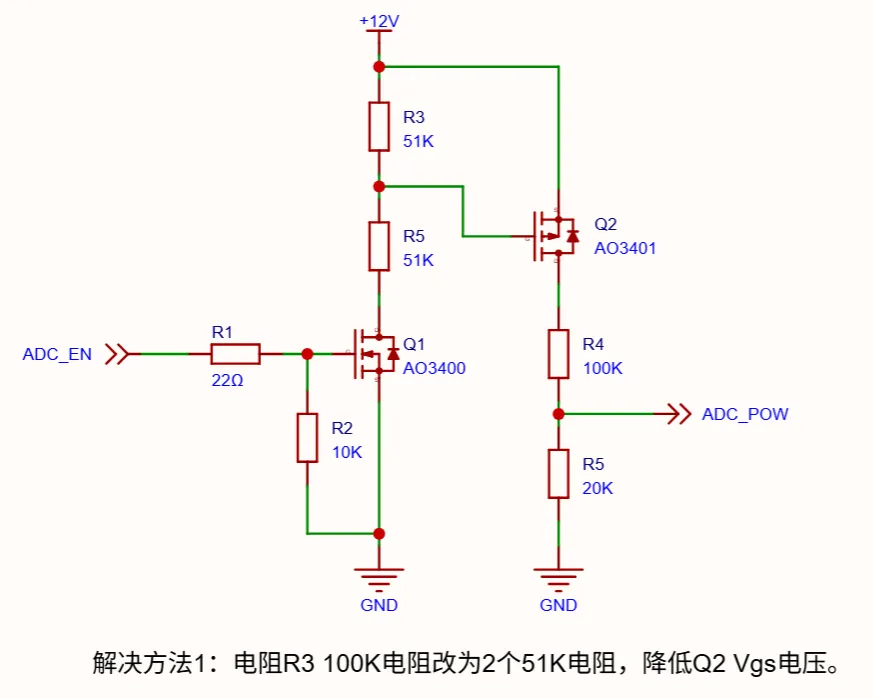

方法 1:电路参数优化(适用于后续产品升级 / 新设计)

核心思路:降低 Q2 导通时的栅源电压 VGS,使其远离耐压极限值,预留足够的安全工作裕量。

核心思路:降低 Q2 导通时的栅源电压 VGS,使其远离耐压极限值,预留足够的安全工作裕量。

具体操作:将原电路中 Q2 栅极上拉电阻 R3(100KΩ)替换为两个 51KΩ 电阻串联的形式,通过分压降低 Q2 栅极上拉电压,使 Q2 导通时的 VGS 绝对值低于 12V,控制在器件耐压安全范围内,从设计层面避免栅源极过压损坏。

具体操作:将原电路中 Q2 栅极上拉电阻 R3(100KΩ)替换为两个 51KΩ 电阻串联的形式,通过分压降低 Q2 栅极上拉电压,使 Q2 导通时的 VGS 绝对值低于 12V,控制在器件耐压安全范围内,从设计层面避免栅源极过压损坏。

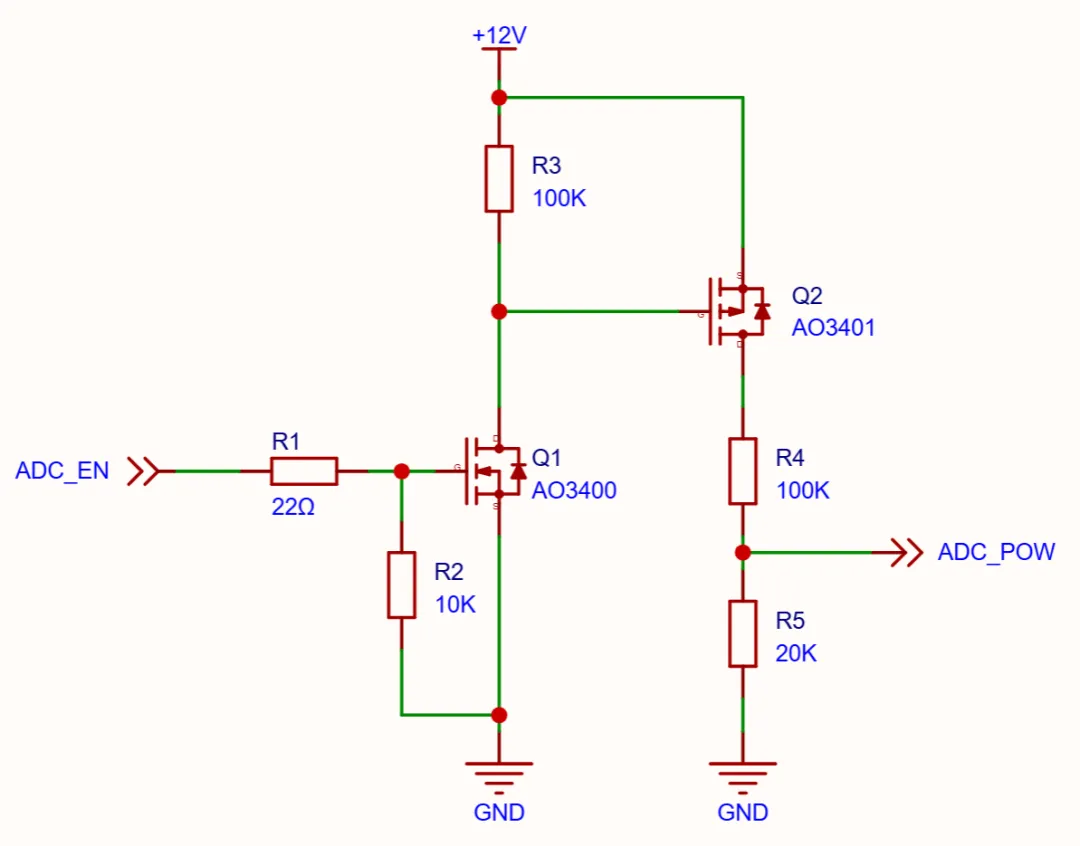

优化后电路:

优化后电路:

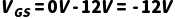

方法 2:更换高耐压 MOS 管(适用于当前量产产品,最优方案)

核心思路:在不改动原有电路布局和参数的前提下,更换栅源耐压更高的 P-MOS 管,匹配电路工作电压,解决过压损坏问题。

核心思路:在不改动原有电路布局和参数的前提下,更换栅源耐压更高的 P-MOS 管,匹配电路工作电压,解决过压损坏问题。

具体操作:将 Q2(AO3401)更换为同封装、栅源耐压更高的 AO3407(栅源耐压为±20V),该型号器件可承受更高的栅源电压,在原电路 Q2 导通时 VGS=-12V 的工况下,工作在安全耐压范围内,不会出现过压损坏,同时同封装的设计无需修改 PCB 板,不会增加量产产品的改造成本,且能快速解决漏电问题。

具体操作:将 Q2(AO3401)更换为同封装、栅源耐压更高的 AO3407(栅源耐压为±20V),该型号器件可承受更高的栅源电压,在原电路 Q2 导通时 VGS=-12V 的工况下,工作在安全耐压范围内,不会出现过压损坏,同时同封装的设计无需修改 PCB 板,不会增加量产产品的改造成本,且能快速解决漏电问题。

替换后电路:

替换后电路: