先跟大家说下基本情况,整个面试下来差不多2小时,全程都在问FPGA相关的专业问题,流程其实很简单,没有什么复杂的环节,就是从自我介绍开始,然后聊项目、问基础、考编程,最后反问了几个问题,一步步来,节奏不算太快,但也不拖沓。

一开始就是常规的自我介绍,不用太复杂,简单说了下自己的专业、学历,重点讲一下自己的项目和实习经历,最好都跟FPGA相关的。这里提醒大家,自我介绍别瞎聊,重点说和岗位相关的,因为后面面试官的问题,全是围绕自我介绍里说的内容问的。

二. 聊项目(最费时间,也最关键)

这部分聊了快1小时,两个面试官都重点问了我项目和实习,问得特别细。

功能,你负责了哪部分,描述整个系统;

具体细节,这部分是怎么实现的;

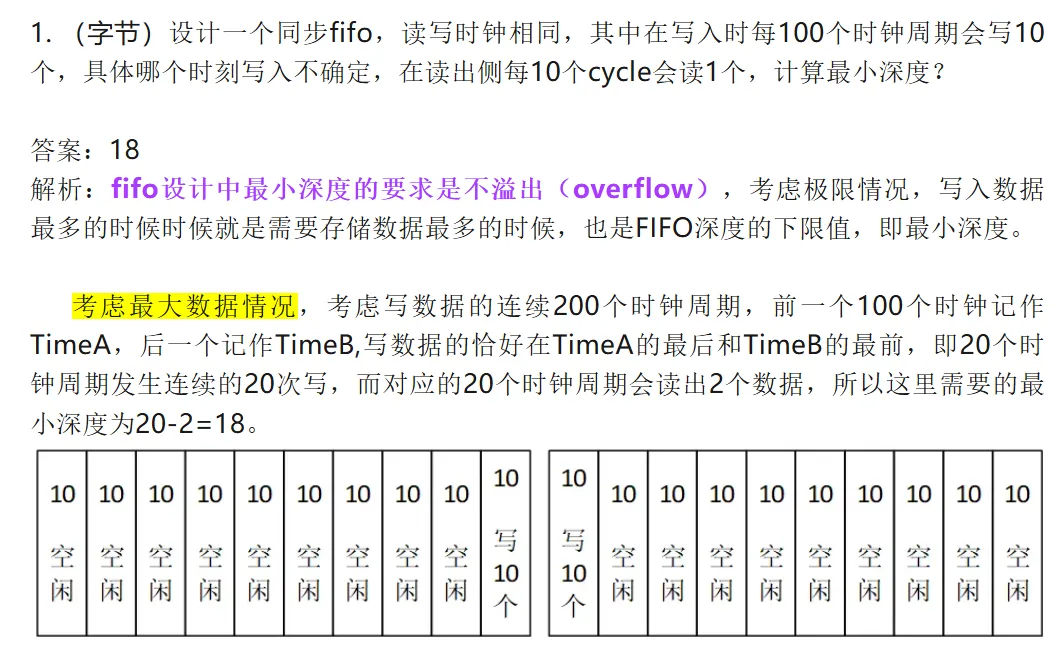

系统中的CDC(跨时钟域)是怎么处理的,你还了解其他的处理方式吗,项目中异步FIFO的深度怎么确定的;

高速接口底层原理,外部呈现的总线或者接口形式是怎样的(AXI-Stream),速率,为什么用RapidIO而不用其他接口,怎么去写的相应的驱动,调试中遇到的问题及解决方式;

HLS和RTL的区别、优势和劣势,项目里哪些用的HLS,哪些用的Verilog;

有没有做软硬件的联合设计和调试,比如以太网之类的,和上层交互;

提到了布线拥塞,问什么会导致布线拥塞;

这里踩了个坑,面试官总问做这个项目的背景、为什么做,有些项目就是老师安排的,没多想,就答得很生硬,大家提前多了解下自己项目的背景,别只盯着自己负责的小模块。

三、 FPGA基础提问

这部分都是基础题,不难,主要就是考平时记的知识点。

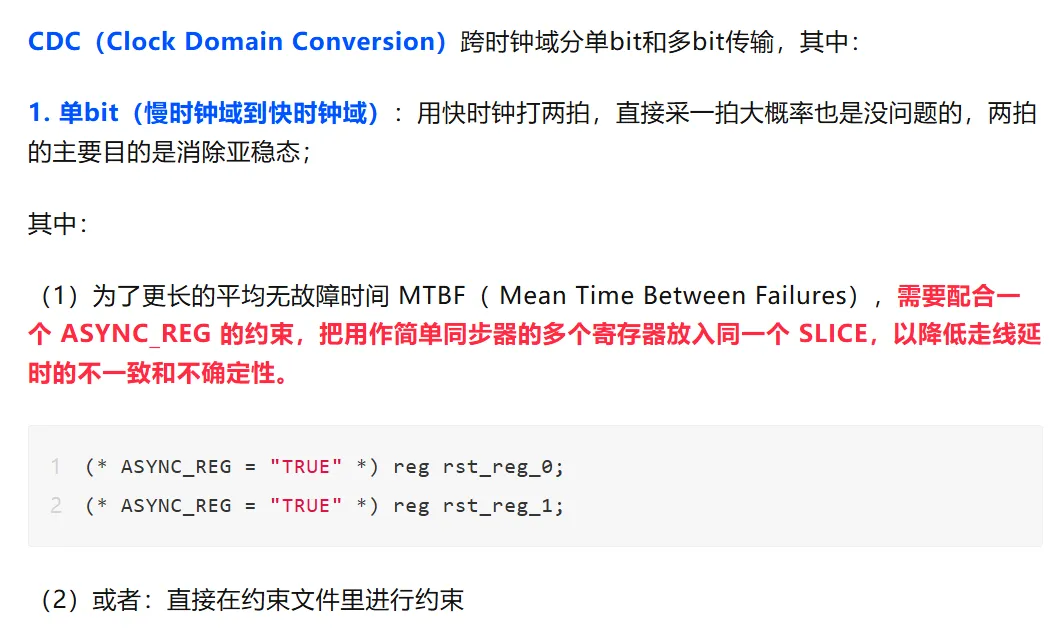

CDC跨时钟域处理方式;

FIFO深度计算;

FPGA底层的资源,除了LUT还有什么;

【答案:Flip-Flop(触发器),Carry Chain进位链,MUX选择器,DSP48,BRAM(Block RAM 块RAM),IOB(IO Bnak 输入输出块),GT高速收发器,ZYNQ里有PS硬核等。】

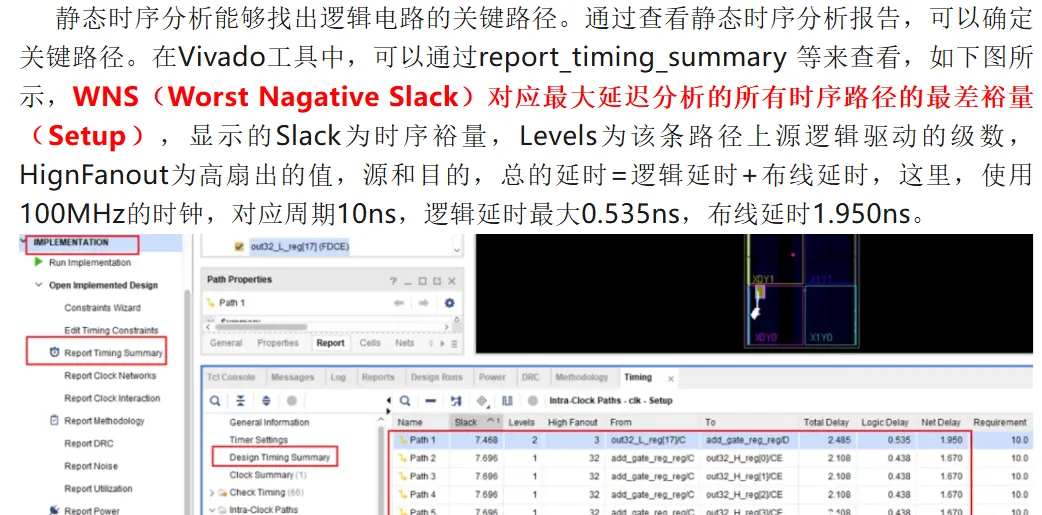

什么是关键路径,怎么处理关键路径;

这部分就捡重点答,比如

跨时钟域单bit用两级触发器,多bit用异步FIFO,约束用set_clock_groups和set_max_delay;

FIFO深度按读写速率差和突发长度算;底层资源还有触发器、进位链、BRAM这些;

关键路径就是延迟最长的路径,优化的话可以改代码、约束时序。

四、一些杂七杂八的提问

这部分就比较简单了,主要是

FPGA能用到哪些地方

能实习多久、每天能来多久

能不能接受指定的实习地点

都是如实回答就好。面试官还问了我之前两段实习的工作时间,看得出来还是比较看重实习稳定性的。

五、手撕代码(重点)

面试最后考了手撕代码,两道题,同步FIFO和序列检测。

同步FIFO:核心实现读写控制、空满判断、数据缓存等功能,这次实操花了25分钟,主要就是实现读写、判断空满这些功能,不算难,但要写得快、写得对

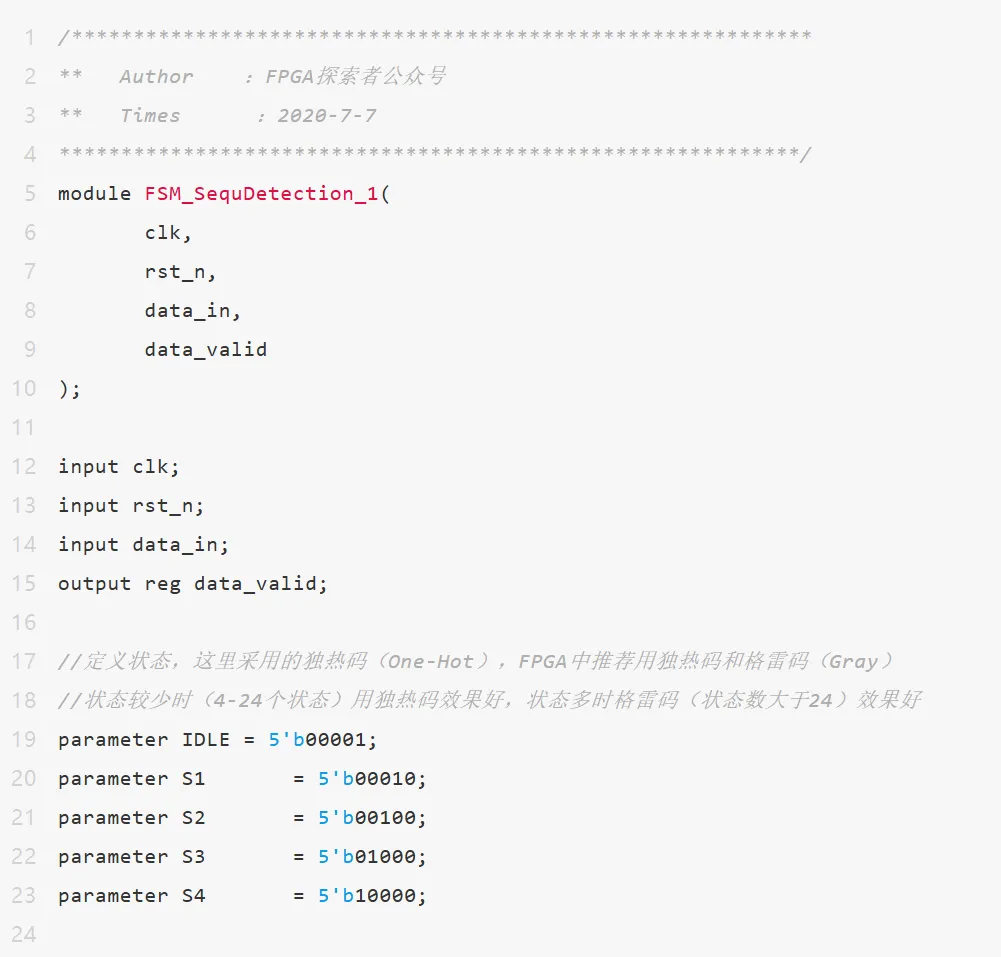

序列检测:采用FSM(有限状态机)实现,重点是状态划分和转移,平时多练练就没问题(为FPGA笔试高频考点)

六. 反问环节

最后我问了面试官,要是顺利入职,实习期间怎么培养我,上手会做什么。

面试官说,大概率是做多个FPGA互联,或者多核CPU在FPGA上的验证

整体难度不算特别高,主要就是考项目细节和基础,还有编程实操。

给27届同学提个醒,提前把自己的项目梳理清楚,不光要会做自己负责的模块,还要了解整个项目的背景;

基础知识点一定要记牢,别临时抱佛脚;手撕代码平时多练,避免面试时手忙脚乱。

武汉至芯后续还会分享更多FPGA面试干货,希望大家都能顺利上岸,拿到自己心仪的实习offer~

还可直接扫描下方二维码,直接领取完整版【字节跳动FPGA实习面试真题资料】,含真题原题、详细解析及答题思路,更有海量FPGA学习干货、前沿行业资讯、独家面试技巧同步放送,帮你少走弯路、高效备考,轻松上岸心仪岗位!

往期精彩: